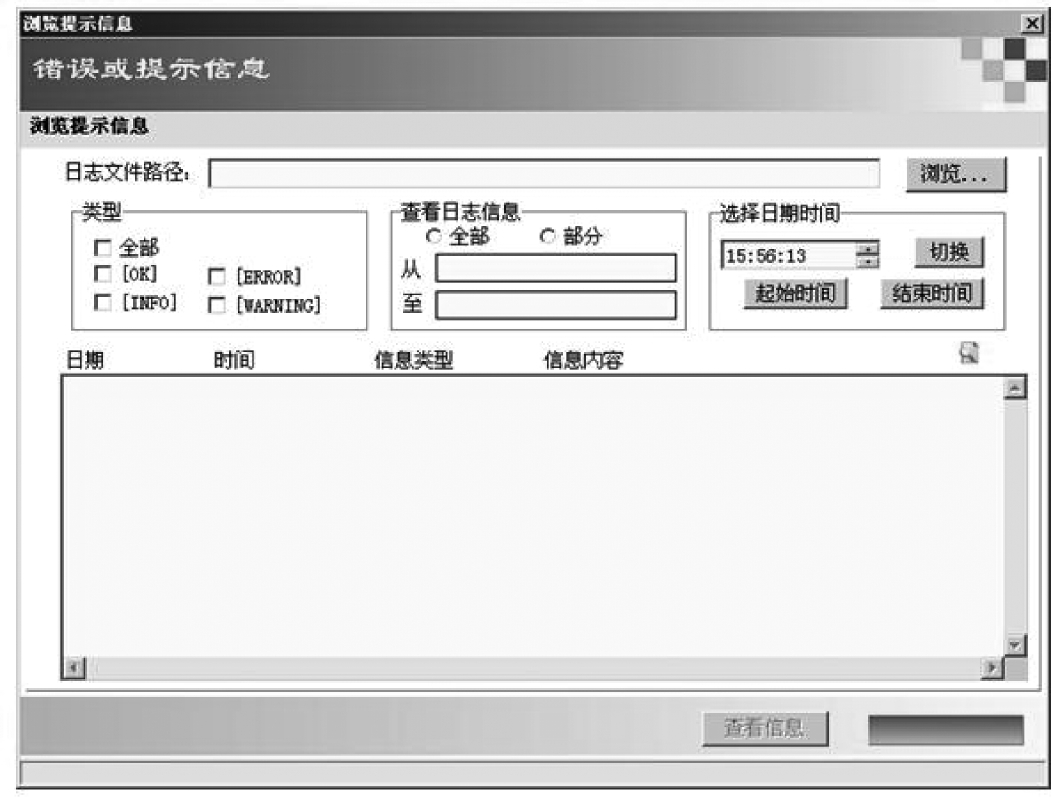

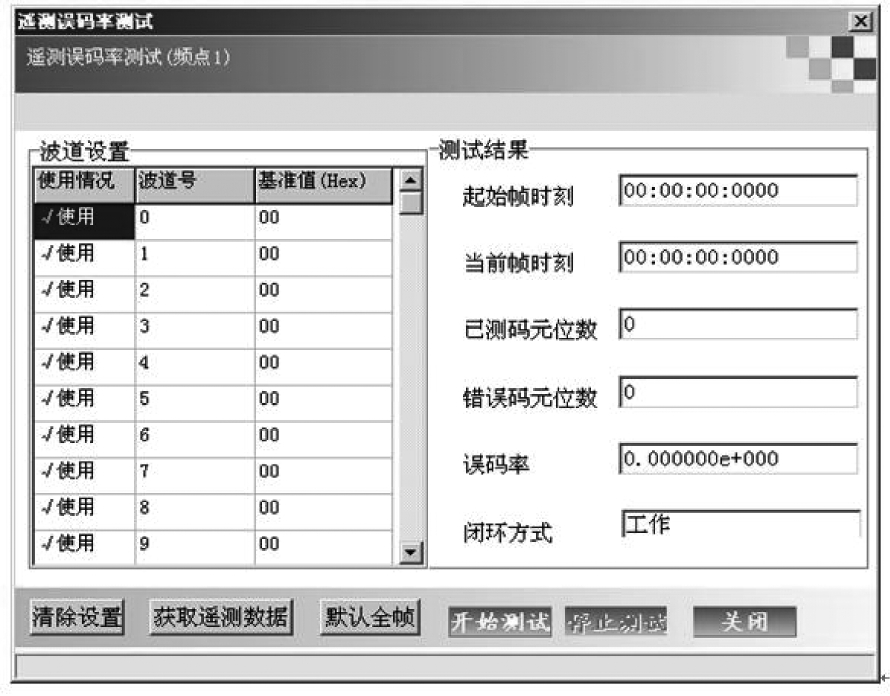

调制器通用信号处理板

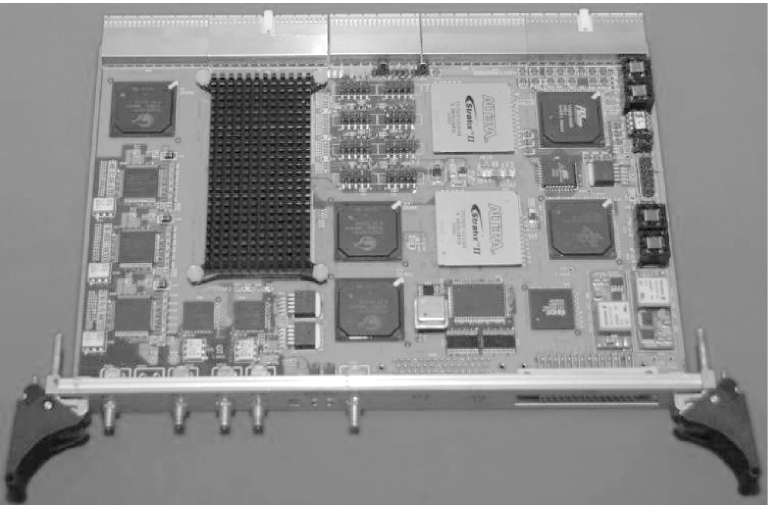

调制器通用信号处理板用于测控基带调制信号和数传基带数传模拟源信号的产生,外观如图5-10所示。

硬件电路主要由以下三部分组成。

1)主控FPGA、PCI接口、双口RAM构成。这一部分主要完成对板卡的功能重组控制,PCI总线数据接收、发送等功能。

2)可重构FPGA和可重构DSP及其外围器件。可重构FPGA加载中频调制器、遥控/遥测模拟源、测距信号产生、小环接收机、噪声源模块。可重构DSP用于各功能单元的控制、遥控处理、模拟源数据注入及部分接收端信号处理等。

图5-10 调制器通用信号处理板实物图

3)2片D/A变换器。D/A变换器工作频率可以到1GHz,可以直接产生70MHz的中频信号;板卡配备2片高速D/A变换器,具备双通道中频调制输出能力。

调制器接口板

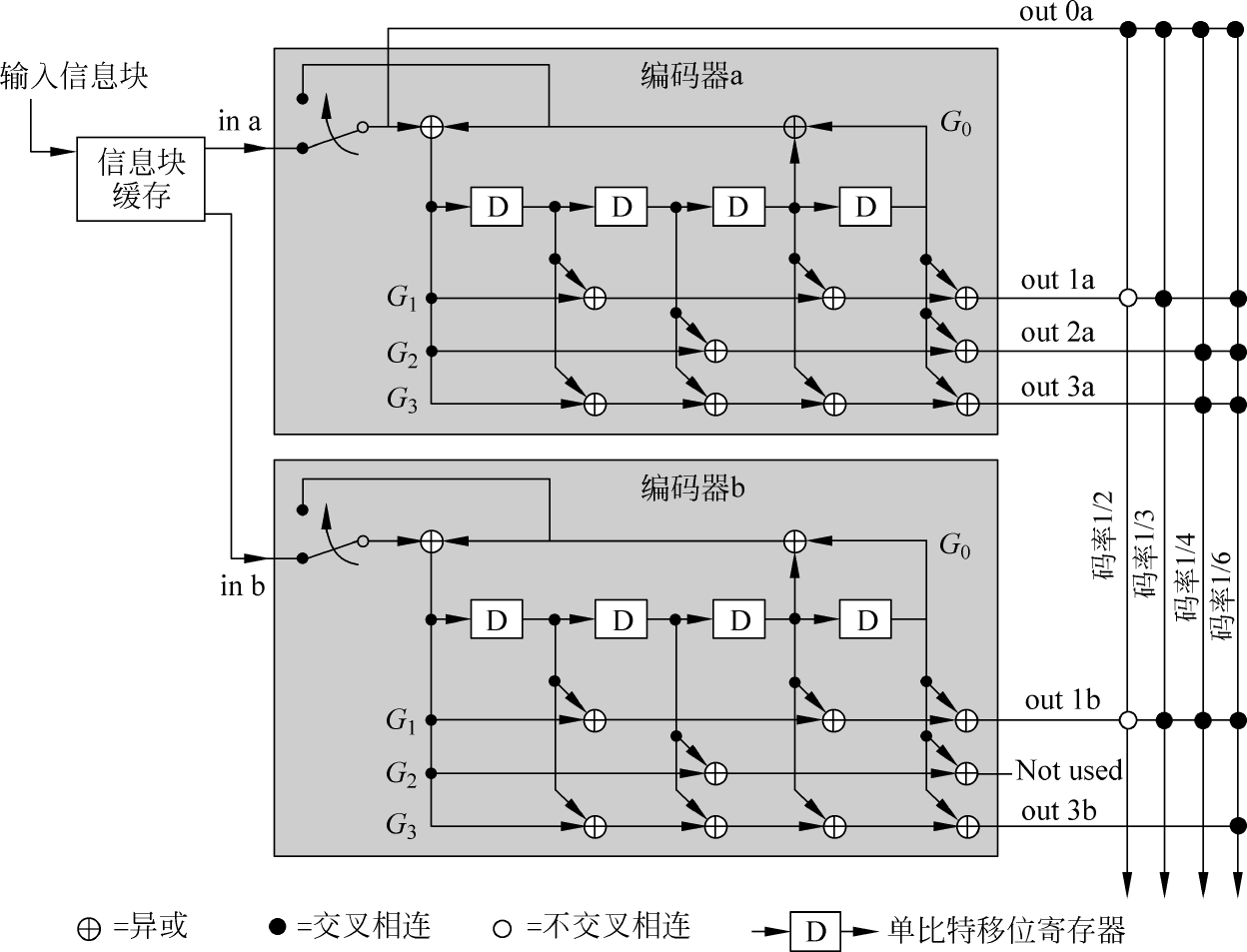

调制器接口板应用于测控基带的上行调制器单元和数传基带的数传模拟源单元。接口板包括:小环接收机通道的滤波放大,A/D变换器,视频卫模接口的D/A变换器,上行中频信道盒(含中频信号调制、白噪声滤波放大、功率调节、信号+噪声、功分器等电路)。电路框图见图5-11。

图5-11 调制器接口板组成框图(除中频信道外)

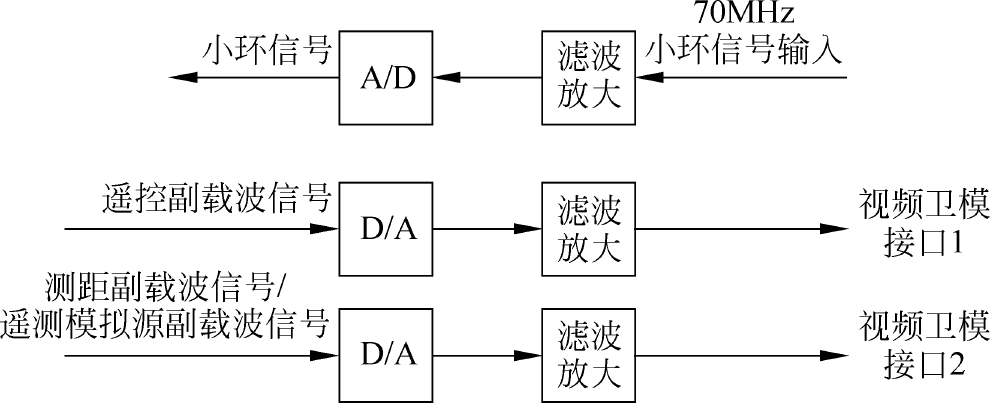

上行中频信道盒电路组成框图如图5-12所示。其中,信号支路的36MHz滤波器用于测控工作状态时调制器上行信号输出;信号支路的40MHz滤波器用于测控信号基带自检或中频闭环时遥测模拟源信号输出、数传信号基带自检或中频闭环时数传模拟源信号输出;噪声支路用于设备自检或中频闭环时加噪信号的噪声输出;卫模支路的5MHz滤波器用于卫模信号输出。

图5-12 上行中频信道盒电路组成框图

下行通用信号处理板

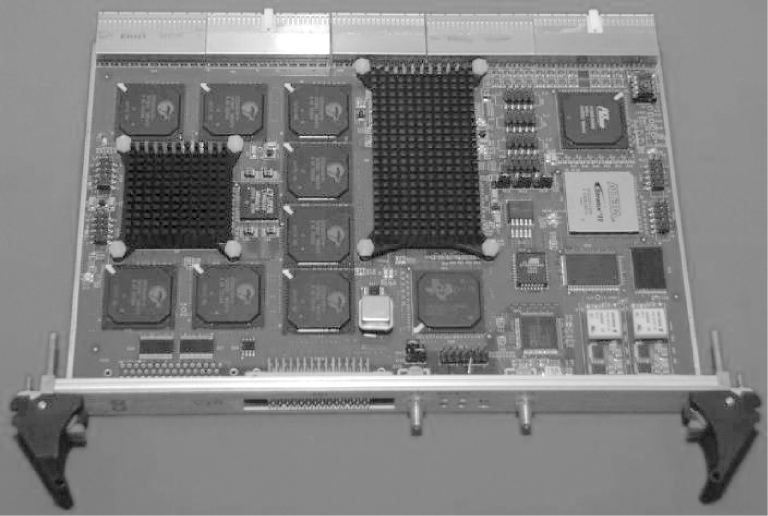

下行通用信号处理板(测控接收机前板和数传接收机前板)。下行通用信号处理板外观如图5-13所示。

图5-13 下行通用信号处理板实物图

硬件电路主要由以下三部分构成。

1)主控FPGA、PCI接口、双口RAM。这一部分主要完成对板卡的功能重组控制,PCI总线数据接收、发送等功能。双口RAM主要用于解调遥测、数传数据缓存上报。

2)可重构FPGA1、FPGA2、FPGA3及其外围器件、可重构DSP及其外围器件、双口RAM。在深空基带中,当本板卡配置为测控基带下行接收机时,FPGA1加载主接收机、测距、测速、遥测等功能模块,FPGA3加载信道译码模块,FPGA2为伪码测距用。当本板卡配置为数传基带下行接收机时,FPGA1加载数传接收机、位同步、帧同步等模块,FPGA3加载信道译码模块。可重构DSP用于各功能单元的控制、部分接收端信号处理等。双口RAM主要用于Turbo译码器的数据存储。

3)3片A/D变换器和2片D/A变换器。A/D变换器采用低电压差动信号(LVDS)电平接口模式,LVDS模式抗干扰能力强,适合高速信号传输,能够较容易地达到210MHz的采样速率,板卡共配备3片高速A/D变换器,具备三通道接收能力;D/A变换器工作频率可以到1GHz,可以直接产生70MHz的中频信号,板卡配备2片高速D/A变换器,具备双通道中频信号输出能力。在深空基带中,每块板卡只完成1个目标下行接收。当板卡配置为测控接收机或数传接收机时,A/D变换器1、2分别输入单目标的左、右旋中频信号,D/A变换器1、2分别输出左、右旋载波接收机锁相环的DCO信号(中心频率25MHz)到跟踪接收机,去除跟踪接收机接收信号多普勒频率。

接收机接口板

接收机接口板应用于测控接收机单元和数传接收机单元,接口板包括下行中频信道盒。中频信道分为3条支路,分别为30MHz、5.4MHz、440kHz的直通支路。其中30MHz支路适用于20dBHz以上接收信噪比,5.4MHz、440kHz支路适用于20dBHz以下接收信噪比。

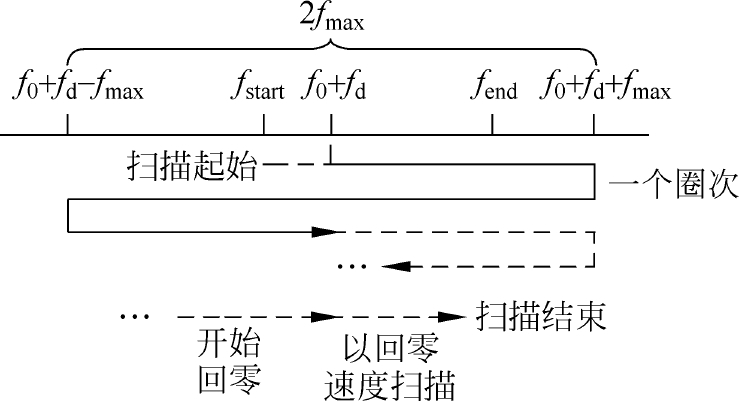

频率捕获单元信号处理板

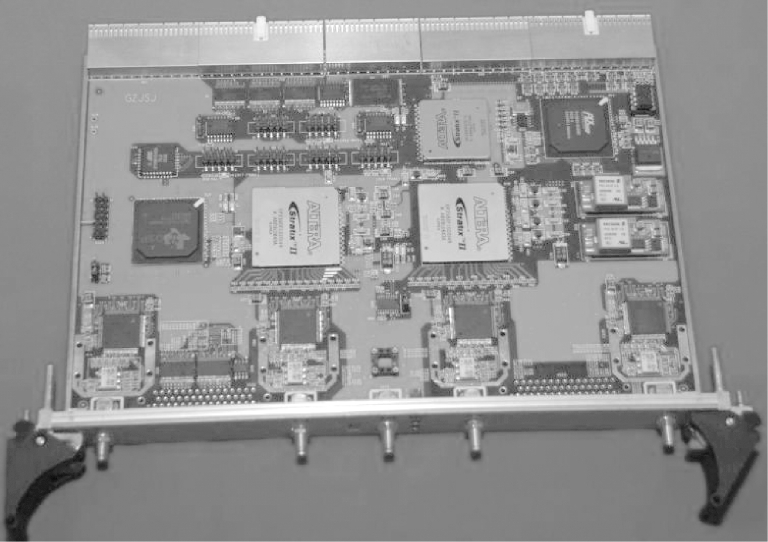

频率捕获单元信号处理板(测控频率捕获板和数传频率捕获板)。频率捕获单元信号处理板外观如图5-14所示。该信号处理板专门针对深空基带极低信噪比高动态下的频率捕获关键专题设计,适用于下行测控、数传信号的频率捕获。

图5-14 频率捕获单元信号处理板实物图

硬件电路主要由以下几部分构成。

1)主控FPGA、PCI接口、双口RAM。这一部分主要完成对板卡的功能重组控制,PCI总线数据接收、发送等功能。

2)可重构FPGA1、FPGA2、FPGA3及其外围器件、DSP及其外围器件、双口RAM、A/D变换器。其中FPGA3连接A/D变换器。输入的中频信号在FPGA2、FRGA3中完成分槽多路数字下变频,变频后数据在双口RAM中缓存,再交FPGA1完成FFT计算。在下变频后的FFT运算环节,由于之前做了数据缓冲,可以实现并行流水线处理,进行高速FFT运算,所以只需要1个FFT模块就可以并行快速处理1000路下变频信号,极大地节约了硬件资源。采用100MHz时钟时,进行1000路信号的16384点FFT处理时间仅160ms。DSP用于单元的参数控制、分槽逻辑控制、各频率槽FFT处理结果的仲裁、判决等功能。

跟踪接收机信号处理板

跟踪接收机信号处理板外观如图5-15所示。该信号处理板专门针对深空基带跟踪接收机关键专题设计。

图5-15 跟踪接收机信号处理板实物图

硬件电路主要由以下几部分构成。

1)主控FPGA、PCI接口、双口RAM。这一部分主要完成对板卡的功能重组控制,PCI总线数据接收、发送等功能。

2)可重构FPGA1、FPGA2及其外围器件、DSP及其外围器件、4片A/D变换器。其中,FPGA1连接A/D变换器1、2,FPGA2连接A/D变换器3、4。接收的左旋和、差中频信号经A/D变换器1、2采样后在FPGA1中完成移相及角误差提取,接收的右旋和、差中频信号经A/D变换器3、4采样后在FPGA2中完成移相及角误差提取,最后在FPGA1中完成极化合成功能,实现角误差解调输出。

跟踪接收机接口板

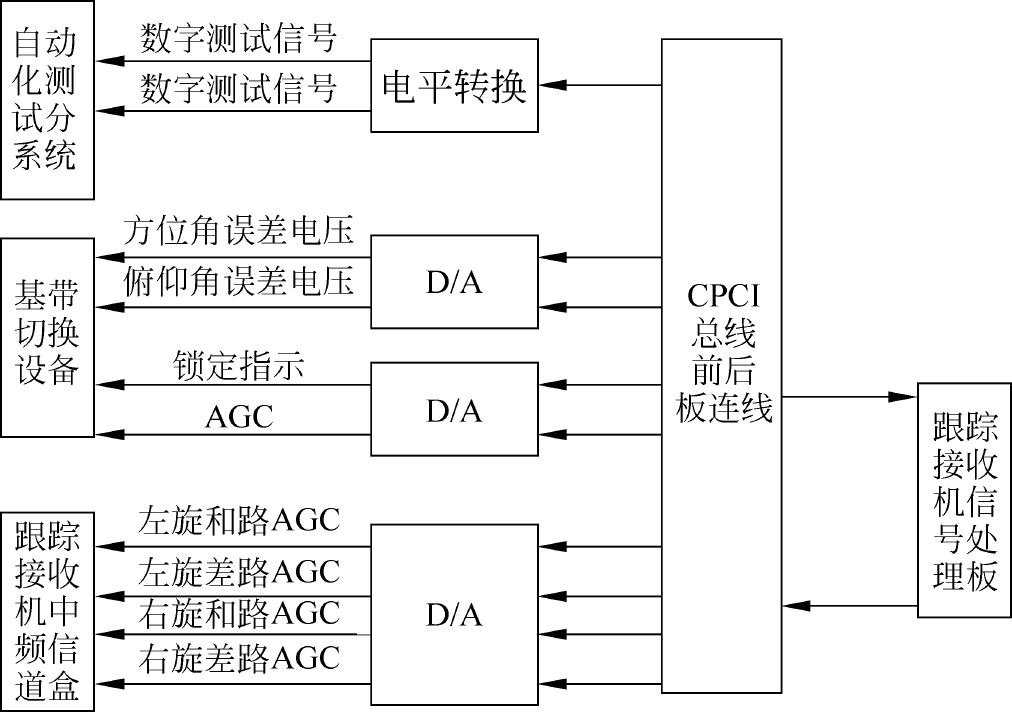

跟踪接收机接口板完成AGC电压的D/A变换,送跟踪接收机中频信道盒;完成角误差电压、AGC电压及锁定指示的D/A变换,送基带切换设备;配合其他分机完成数字测试信号的电平转换输出,送自动化测试分系统。其电路框图见图5-16。

图5-16 跟踪接收机接口板电路框图

跟踪接收机中频信道盒

跟踪接收机中频信道盒完成左、右旋和差通道中频信号的混频、滤波、AGC放大功能。中频信道盒原理框图见图5-17。