原理简述

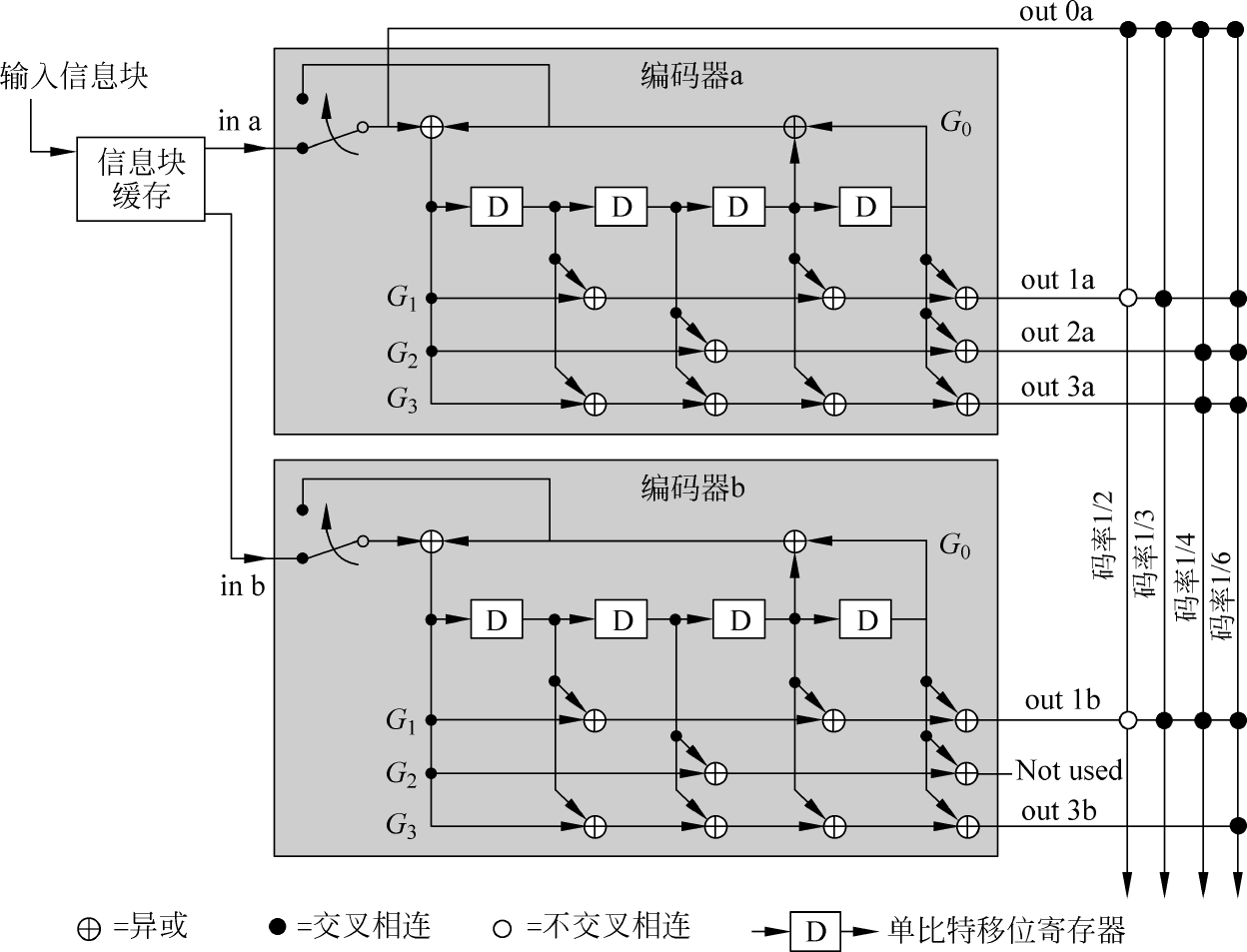

频综模块原理框图如图3-13所示。本方案采用直接数字合成器(DDS)正交混频+PLL的方法实现。主要由倍频单元、本振环、DDS正交混频单元、跟踪环、控制单元等构成。

图3-13 频综模块原理框图

1)倍频单元:为本振环提供参考源以及为DDS提供时钟。对输入参考源10MHz通过三极管放大倍频到50MHz,作为本振环的参考源;分出一路50MHz继续三极管放大倍频到300MHz,作为DDS时钟。

2)本振环:为DDS正交混频提供可变本振。由于DSF1对1Hz处相噪要求很高,根据前期实验结果,采用Hittite公司的电压型低噪声PLL器件,才能够获得较低的近载端相噪。本振环输出频率850/900MHz。

3)DDS正交混频单元:为跟踪环提供参考信号。DDS输出频率10~60MHz,混频后输出835~885MHz。

4)跟踪环:跟踪滤波,采用Hittite公司的电压型低噪声PLL器件,输出频率1670~1770MHz。

5)控制单元:控制本振环和DDS。

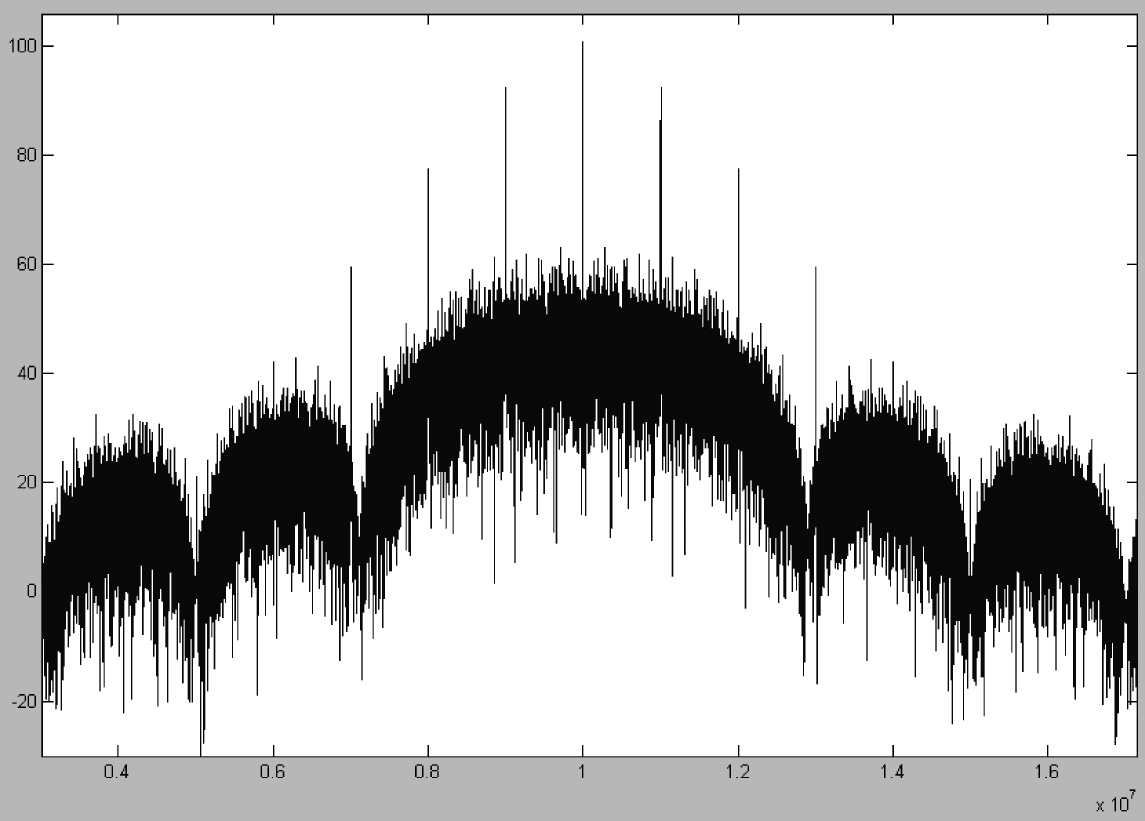

相噪分析计算

环路带宽内的相噪取决于输入参考源的相噪和PLL自身的噪声基底,环路带宽外的相噪取决于VCO相噪。在PLL环路带宽内,参考信号和鉴相器引入的噪声由如下计算得到:

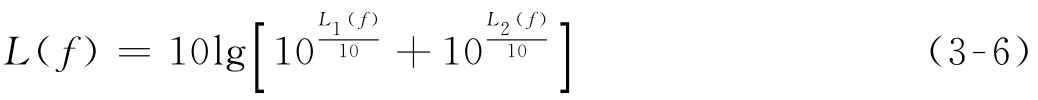

参考信号的相位噪声对输出信号相噪的贡献:

式中 Lr(f)——输入参考的相位噪声(dBc/Hz)。

鉴相器的基底相噪对输出信号相噪的贡献:

式中 LPD(f)——鉴相器的基底相噪(dBc/Hz);

Fc——鉴相频率。

因此,在环路带内输出信号的相位噪声L(f)(dBc/Hz)可由下式得到:

频综输出信号采用DDS正交混频+跟踪环方案。以最高输出频率1770MHz为例,本振频率为900MHz,DDS频率为15MHz,由于DDS的频率远低于本振频率,混频输出信号的相噪由本振信号相噪决定。跟踪环是2倍频,理论上对相噪恶化6dB。本振环鉴相频率为50MHz,倍频次数18次,理论恶化25dB。环路带宽取126kHz,相位余量取64°,可以得到最终输出信号的相噪指标,如表3-2所示。

表3-2 频综相噪指标分析表 单位:dBc/Hz

注:①晶体滤波器对10kHz及10kHz以外的相噪有改善;②鉴相器1/F噪底曲线影响;③环路带宽边沿影响;④1.5MHz DDS信号几乎无影响。

谐波抑制

谐波抑制靠输出低通滤波器(LPF)保证,实际谐波抑制大于60dB。

杂波计算

频综杂散的主要来源为DDS杂散、环路鉴相杂散、正交混频杂散。

1)DDS杂散。查DDS器件(AD9854)手册可知,窄带杂散典型值为-85dBc左右,由于跟踪环是1:1输出,DDS杂散不会恶化。因此,DDS杂散满足指标要求。

2)环路鉴相杂散。本振环和跟踪环都是窄带环,鉴相泄漏应在75dBc以上,满足指标。

3)正交混频杂散。正交混频器的镜频抑制有20dBc,由于混频信号直接作为跟踪环的参考信号,跟踪环是窄带环,因此,混频后的杂散都被环路滤波器滤掉。杂散抑制应在75dB以上。